# MOS only oscillator using adder and subtractor circuits

Merih Yıldız<sup>1</sup>, Cem Göknar<sup>2</sup>, and Shahram Minaei<sup>1</sup>

1Dept. of Electronics and Communications Engineering, Dogus University, Acibadem 34722, Istanbul, Turkey. 2EE Dept., Işık University, Şile 34980, İstanbul, Turkey

myildiz@dogus.edu.tr, cem.goknar@isikun.edu.tr, and sminaei@dogus.edu.tr

### **Abstract**

In this paper an NMOS based sinusoidal oscillator is presented. The circuit is constructed with voltage-mode (VM) NMOS-based analog adder and subtractor circuits which respectively perform  $V_1+V_2$  and  $V_1-V_2$  operations on the input voltages. The most important feature of the proposed circuits is their extremely simple structures containing only twelve NMOS transistors (six for the adder, six for the subtractor). Another significant advantage of the proposed circuits is that no external passive components are being used. The post-layout simulations of the proposed oscillator circuit have been executed using TSMC 0.25  $\mu m$  process parameters with  $\pm 1.25$  V power supply voltage.

### 1. Introduction

Oscillator circuits are widely used in communication circuits, instrumentation, measurement, etc. There are many oscillator circuits available in the literature using various active elements [1-11]. For example in [1] a sinusoidal oscillator using two current controlled current differencing transconductance amplifiers (CCCDTAs) as active elements and two grounded capacitors is presented. Similarly, other active elements such as second generation current conveyors (CCIIs), operational transconductance amplifiers (OTAs), differential voltage current conveyors (DVCCs) etc, have been used to construct sinusoidal oscillators [2-11]. All of the above mentioned oscillator circuits require passive elements such as resistors and capacitors which increase the power consumption and the silicon area in integrated circuit (IC) fabrication.

In this work, a new sinusoidal oscillator circuit using only one adder and one subtractor circuit [12] as active elements is presented. The most important feature of the circuit is that no passive element is required. However an external capacitor can be added to change the oscillation frequency. It is interesting to observe that the topology of the mutative 4-port, introduced in [12], augmented by two simple external feedback paths between its ports creates an oscillator in addition to many applications demonstrated in [12] and [13].

The paper is organized as follows. The proposed oscillator circuit and its analyses are given in Section 2. Simulation results of the proposed circuits are presented in Section 3. Finally, some concluding remarks are discussed in Section 4.

## 2. Proposed Oscillator Circuit

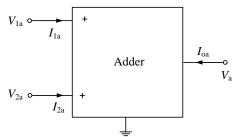

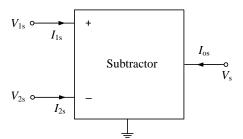

The symbol for the analog adder and subtractor circuits are shown in Fig. 1 and Fig. 2, respectively. The input terminals of the adder  $(V_{1a},V_{2a})$  and subtractor  $(V_{1s},V_{2s})$  circuits exhibit high impedance while the output terminals  $(V_a,V_s)$  exhibit low

impedance. The ideal input-output relations of the adder and subtractor circuits are:

$$V_{0a} = V_{1a} + V_{2a} \tag{1}$$

$$V_{os} = V_{1s} - V_{2s} (2)$$

together with  $I_{1a} = I_{2a} = I_{1s} = I_{2s} = 0$ .

In the non-ideal case the expressions take the form:

$$V_{oa} = k_1 V_{1a} + k_2 V_{2a} \tag{3}$$

$$V_{0S} = k_3 V_{1S} - k_4 V_{2S} \tag{4}$$

here  $k_i$  (i=1,2,3,4) is the non-ideality coefficient of the adder and subtractor circuits depending on the threshold voltages and aspect ratios of the transistors. A detailed analysis of the non-ideality coefficients is given in [12].

Fig. 1. Symbol of the analog adder circuit

Fig. 2. Symbol of the analog subtractor circuit

## A. The Proposed MOS only Oscillator

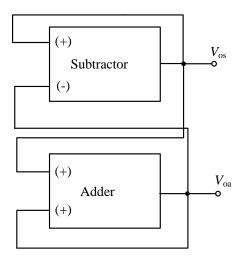

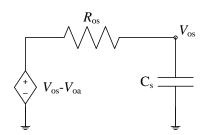

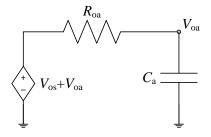

The proposed MOS only oscillator circuit constructed with an analog adder and a subtractor is given in Fig. 3. In order to find the theoretical operating frequency of the oscillator, simplified equivalent circuits of the subtractor and adder blocks including the feedback connections between the ports are shown respectively in Fig. 4 and Fig. 5.

In Fig.4 and Fig.5  $R_{\rm os}$  and  $R_{\rm oa}$  represent the output resistances and,  $C_{\rm s}$  and  $C_{\rm a}$  are the equivalent parasitic capacitances at the output nodes of the subtractor and adder circuits. Replacing Fig. 4 and Fig. 5 in Fig. 3, the matrix state equation in (7) can be derived:

$$C_S \frac{dV_{os}}{dt} = \frac{V_{os} - V_{oa} - V_{os}}{R_{os}} = \frac{-V_{oa}}{R_{os}}$$

(5)

$$C_a \frac{dV_{oa}}{dt} = \frac{V_{os} + V_{oa} - V_{oa}}{R_{oa}} = \frac{V_{os}}{R_{oa}}$$

(6)

$$\frac{d}{dt} \begin{bmatrix} V_{oa} \\ V_{os} \end{bmatrix} = \begin{bmatrix} 0 & \frac{1}{C_a R_{oa}} \\ \frac{-1}{C_s R_{os}} & 0 \end{bmatrix} \begin{bmatrix} V_{oa} \\ V_{os} \end{bmatrix}$$

(7)

The eigenvalues  $\lambda_{1,2}$  of the matrix in (7), are:

$$\lambda_{1,2} = \pm j \sqrt{C_s C_a R_{oa} R_{os}} \tag{8}$$

and the operating frequency of the oscillator is obtained as:

$$f = \frac{1}{2\pi\sqrt{C_sC_aR_{oa}R_{os}}}\tag{9}$$

Fig. 3. Oscillator circuit

Fig. 4. Equivalent circuit of the subtractor block.

Fig. 5. Equivalent circuit of the adder block.

### B. Tunable Oscillator Circuit

The proposed MOS only oscillator circuit can be frequency tuned by connecting an external capacitor to either the output node of the adder or the subtractor circuits. If a capacitor C is connected to the output port of the adder, from an equation similar to (7) derived in part A. the operating frequency of the tunable oscillator is obtained as:

$$f = \frac{1}{2\pi\sqrt{C_s(C_a + C)R_{oa}R_{os}}}$$

(10)

Similarly if the external capacitor C is connected to the output port of the subtractor the operating frequency of the tunable oscillator is again obtained as:

$$f = \frac{1}{2\pi\sqrt{(C_S + C)C_aR_{oa}R_{os}}}.$$

(11)

## 3. Simulation results of the oscillators

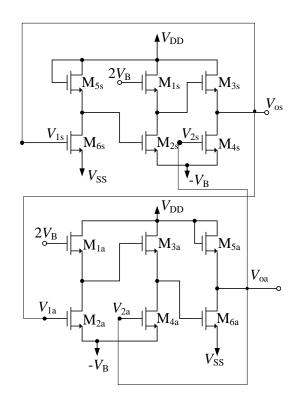

The schematic of the proposed oscillator circuit is shown in Fig. 6. In Fig. 6  $V_{1s}$ ,  $V_{2s}$  show the inputs of the subtractor and  $V_{1a}$  and  $V_{2a}$  show the inputs of the adder circuit. The dimensions of the MOS transistors in Fig. 6. are given in Table 1. The output resistances of the subtractor and adder blocks are found as:

$$R_{os} \cong \frac{1}{g_{m3s}} \tag{12}$$

and

$$R_{oa} \cong \frac{1}{g_{m5a}} \tag{13}$$

respectively. Here  $g_{m3s}$  and  $g_{m5a}$  are the transconductances of the transistors  $M_{3s}$  and  $M_{5a}$  respectively.

For theoretical results the output resistors in Fig. 6 are calculated as  $R_{\rm os}$ =2.2 k $\Omega$  and  $R_{\rm oa}$ =2 k $\Omega$  from expressions (12) and (13). The parasitic capacitors  $C_{\rm s}$ =73 fF and  $C_{\rm a}$ =71 fF are obtained from the post-layout simulation. Using these resistor and capacitor values the operating frequency is obtained as 1050 MHz from expression (9).

Fig. 6. The schematic of proposed oscillator circuit.

Table 1. Dimensions of MOS transistors for oscillator circuit

| Transistors                               | W[µm] | L[μm] |

|-------------------------------------------|-------|-------|

| $M_{1a}, M_{2a}, M_{3a}, M_{4a}$          | 1     | 0.5   |

| $M_{5a}$ , $M_{6a}$                       | 30    | 0.5   |

| $M_{1s}$ , $M_{2s}$ , $M_{5s}$ , $M_{6s}$ | 1     | 0.5   |

| $M_{3s}, M_{4s}$                          | 30    | 0.5   |

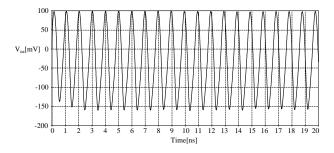

The output waveform resulting from the post layout simulation of the circuit in Fig. 6 is given in Fig. 7. The simulation results of the oscillator circuit show oscillations at 1000 MHz; so, the theoretical and simulation results are in a very good agreement.

Fig. 7. Simulation result of the oscillator circuit

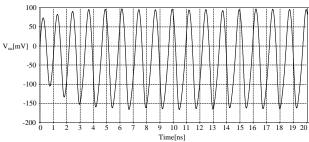

An external capacitor C=60 fF is connected to the output node of the adder circuit. The theoretical operating frequency of the tuned oscillator is obtained as 750MHz from the expression (10). The simulation result of the tuned oscillator show

oscillations at 770MHz as shown in Fig. 8. Thus theoretical and simulation results are again in a good agreement.

Fig. 8. Simulation result of the oscillator with external capacitor

### 4. Conclusions

In this paper using the recently introduced the generalized mutator 4-port built with an adder and a subtractor block [12], a new realization for an oscillator has been presented. With this oscillator application in addition to previously demonstrated ones such as mutator, inverter, gyrator, filter etc. circuits [12,13] the universality of the 4-port is being clearly established.

By connecting an external capacitor to the output of the adder or the subtractor circuit the oscillation frequency of the proposed oscillator can be tuned. Post-layout simulations of the proposed circuit are done with SPICE using TSMC 0.25  $\mu m$  process technology parameters. Comparisons of SPICE simulated versus theoretical values are also presented which show a very good agreement.

## 5. References

- [1] W. Jaikla, A. Lahiri, "Resistor-less current-mode fourphase quadrature oscillator using CCCDTAs and grounded capacitors", *International Journal of Electronics and Communications (AEU)*, vol. 66, no. 3, pp. 214–218, 2011.

- [2] R. Sotner, Z. Hrubos, B. Sevcik, J. Slezak, J, Petrzela, T, Dostal, "An example of easy synthesis of active filter and oscillator using signal flow graph modification and controllable current conveyors", *Journal of Electrical Engineering*, vol. 62, no. 5, p. 258–266, 2011.

- [3] J.W. Horng, H. Lee, J. Wu, "Electronically tunable third-order quadrature oscillator using CDTAs", *Radioengineering*, vol. 19, no. 2, pp. 326–330, 2010.

- [4] A. Kwawsibsam, B. Sreewirote, W. Jaikla, "Third order voltage mode quadratrue oscillator using DDCC and OTAs", In *International Conference on Circuits, System and Simulation (IPCSIT)*, Singapore, 2011, vol. 7, pp. 317–321.

- [5] J. Galan, R. G. Carvajal, F. Munoz, A. Torralba, J. Ramirez-Angulo, "A low-power low-voltage OTA-C sinusoidal oscillator with more than two decades of linear tuning range" In *Proc. of the 2003 International Symposium on Circuits and Systems*, Bangkok (Thailand), 2003, vol. 1, pp. 677–680.

- [6] P. Beg, M. A. Siddiqi, M. S. Ansari, "Multi output filter and four phase sinusoidal oscillator using CMOS DX-MOCCII", *International Journal of Electronics*, vol. 98, no. 9, pp. 1185 – 1198.

- [7] H. C. Chien, "Voltage- and current-modes sinusoidal oscillator using a single differential voltage current conveyor", *Journal of Applied Science and Engineering*, vol. 16, no. 4, pp. 395-404, 2013.

- [8] D. Biolek, A. Ü. Keskin, V. Biolkova, "Grounded capacitor current mode single resistance-controlled oscillator using single modified current differencing transconductance amplifier", *IET Circuits, Devices & Systems*, vol. 4, no. 6, pp. 496–502, 2010.

- [9] Y. LI, "A new single MCCCDTA based Wien-bridge oscillator with AGC", *International Journal of Electronics and Communications* (AEU), vol. 66, no. 2, pp. 153–156, 2012.

- [10] M. Sagbas, U. E. Ayten, N. Herencsar, S. Minaei, "Current and Voltage Mode Multiphase Sinusoidal Oscillators Using CBTAs", *Radioengineering*, vol. 22, no.1, pp. 24-33, 2013.

- [11] S. A. Tekin, H. Ercan, M. Alçi, "A Versatile Active Block: DXCCCII and Tunable Applications", Radioengineering, vol. 23, no.4, pp. 1130-1139, 2014

- [12] S. Minaei, İ. C. Göknar, M. Yildiz, and E. Yuce, "Memstor, Memstance Simulations via a Versatile 4-port Built with New Adder and Subtractor Circuits," *International Journal* of *Electronics*, vol. 102, no. 6, pp. 911-931, 2015, published online July 6, 2014.

- [13] İ.C. Göknar, and E. Minayi, "Realizations of Mutative 4-ports and their Applications to Memstor Simulations", *Analog Integrated Circuits and Signal Processing*, Springer vol. 81, no. 1, pp. 29-42, 2014.